| Hohe Genauigkeit |  |

| Kleine Größe | |

| Hohe Tracking-Geschwindigkeit | |

| Unterbrechungsfreies Tracking während der Datenübertragung | |

| Latch-Ausgang mit drei Zuständen | |

| Energieeffizient |

Ausgangssignal ist paralleler natürlicher Binärcode, der durchgepuffert wird | Latch mit drei Zuständen und kompatibel mit TTL-Pegel. |

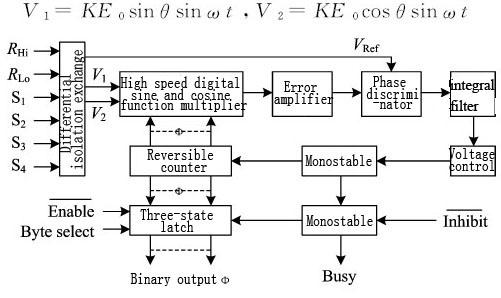

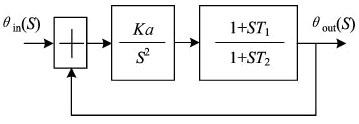

Das Produkt wendet eine Servoschaltung zweiter Ordnung mit geringer Größe und geringem Gewicht an | |

Gewicht, und der Benutzer kann es sehr bequem durch Steuern verwenden | |

Signalstifte. | |

Tabelle 2 Nennbedingungen und empfohlene Betriebsbedingungen | max. absoluter Bewertungswert |

Versorgungsspannung +VS: 12,5~17,5V | |

Versorgungsspannung -VS: -17,5~-12,5V | |

Logische Spannung VL: 7V | |

Lagertemperaturbereich: -40~+100℃ | |

Empfohlene Betriebsbedingungen |

Referenzspannung (Effektivwert) VRef: Nennwert ±10 % | Signalspannung (Effektivwert) V1*: Nennwert ±10 % Bezugsfrequenz f*: Nennwert ±10 % | Betriebstemperaturbereich TA: -40~+85℃ | Hinweis: * gibt an, dass es gemäß den Anforderungen des Benutzers angepasst werden kann. | |

Tabelle 2 Elektrische Eigenschaften | Parameter | |||

Bedingungen (-40~+85℃) | (Falls nicht anders angegeben) | 12 | 16 | (Serie MSDC/MRDC37) |

Einheit | – | 3 | 36 | Mindest. |

max. | Auflösung/RES | Bereich von 0~360º | – | V |

Bit | Tracking-Geschwindigkeit/St① | – | rps | V |

Hoher Ausgangspegel/VOH | TAu003d25℃ | – | 2.4 | W |

Niedriger Ausgangspegel/VOL | TAu003d25℃ | – | 0,8 | % |

Stromverbrauch/ PD | – | 2 | TAu003d25℃ | V |

1.3 | – | 2 | 90 | V |

Vel-Linearität/ERl | – | 30 | TAu003d25℃ | Hz |

1.0 | – | ±3 | Bereich der Referenzspannung | 115 |

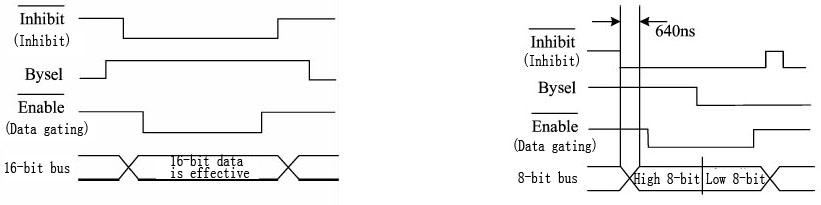

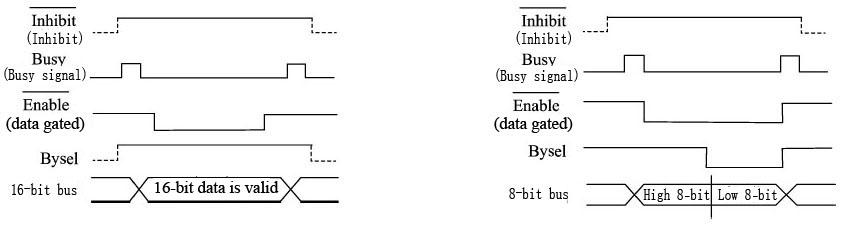

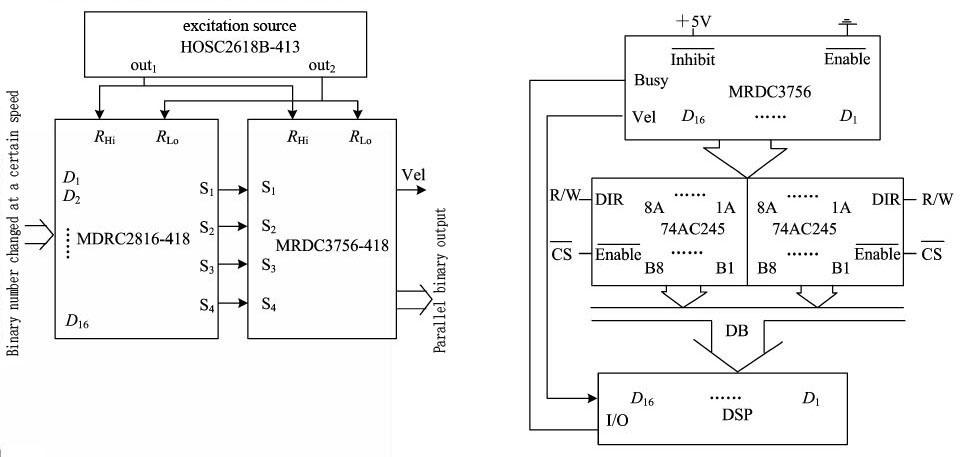

B: Der Konverter ist mit dem 8-Bit-Bus verbunden, die Bits D1 bis D8 sind mit dem Datenbus verbunden und der Rest ist leer. | Setzen Sie Sperren von logisch 1 auf logisch 0 (Datensperre) und warten Sie 1 μs; setze Enable auf logisch 0, damit der Latch im Konverter Daten ausgeben kann; einstellen | Bysel auf logisch 1, die hohen 8-Bit-Daten direkt lesen, Bysel auf setzen | logisch 0, lese die Daten in anderen Bits mit automatischer Nullauffüllung | die freien Bits; auf logisch 1 setzen, um sich auf das Lesen der nächsten effektiven Daten vorzubereiten (Fig. 5). | Hemmen | Abb. 4: Zeitliche Abfolge der 16-Bit-Busübertragung Abb. 5: Zeitliche Abfolge der 8-Bit-Busübertragung | (2) Busy-Methode (asynchrones Lesen): | Im asynchronen Lesemodus wird Inhibit auf logisch 1 oder leer gesetzt, ob die interne Schleife immer in der ist |

1 | D1 | stabiler Zustand oder ob die Ausgangsdaten gültig sind, soll bestimmt werden | 13 | durch den Status des Besetztzeichens Besetzt. Wenn das Besetztsignal hoch ist | Ebene zeigt es an, dass die Daten konvertiert werden, und die Daten auf dieser Ebene | 25 | Zeit ist instabil und ungültig; wenn das Besetztsignal auf niedrigem Pegel ist, es | zeigt an, dass die Datenkonvertierung abgeschlossen ist, und die Daten dabei |

2 | D2 | Zeit ist stabil und gültig. Sobald während des Lesens ein hoher Pegel in Busy auftritt, | 14 | die Lesung zu diesem Zeitpunkt ist ungültig. Im asynchronen Lesemodus wird die | Der Busy-Ausgang ist eine Impulsfolge mit TTL-Pegel, seine Breite hängt davon ab | 26 | Drehzahl gibt es auch zwei Verwendungsmethoden des Busses, nämlich 8-Bit | und 16-Bit ist auch das Datenlesen während der effektiven Datenausgabe |

3 | D3 | gesteuert durch Enable , entnehmen Sie bitte dem Zeitablaufdiagramm für die Datenübertragung (Abb. 6 und Abb. 7). | 15 | Abb.6 Zeitablaufdiagramm für 16-Bit-Busübertragung. Abb.7 Zeitablaufdiagramm für 8-Bit-Busübertragung | Statussignalpins: Besetzt, DIR, R, C. | 27 | Wenn sich der Eingang des Konverters ändert, gibt Busy eine Impulsfolge aus | des CMOS-Pegels wird seine Frequenz durch die höchste Rotation bestimmt |

4 | D4 | Geschwindigkeit. Wenn Busy auf High-Pegel ist, bedeutet dies den Servo zweiter Ordnung | 16 | Schaltung im Konverter arbeitet, die Daten am digitalen Ausgangsende sind | Ändern; im Gegenteil, der Computer kann die Daten direkt lesen. | 28 | Das DIR-Signal wird verwendet, um die Vorwärts-/Rückwärtsdrehung anzuzeigen. Bei der Ausgabe | |

5 | D5 | Code ist aufwärts gezählt, der Ausgang ist High-Pegel; wenn der Ausgangscode ist | 17 | NC | Abwärtszählen, der Ausgang ist Low-Pegel. | 29 | Nullsignalausgang R.C: wenn die Ausgangsdaten von allen 1 auf inkrementieren | alle 0, oder die Ausgangsdaten werden von allen 0 auf alle 1 dekrementiert, die |

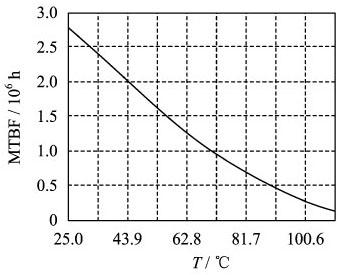

6 | D6 | Ausgang ist positiver Impuls, die Impulsbreite beträgt 200 μs. | 18 | 5. MTBF-Kurve von Synchro-Digital-Wandlern oder Resolver-Digital-Wandlern (MSDC/MRDC37-Serie) (Abb. 7) | Abb. 8 MTBF-Temperaturverlauf | 30 | (Hinweis: nach GJB/Z299B-98, gute Bodenbeschaffenheit vorausgesetzt) | |

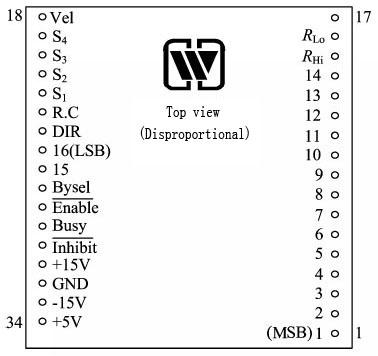

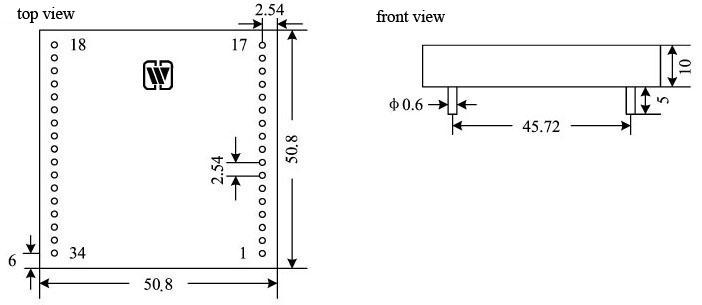

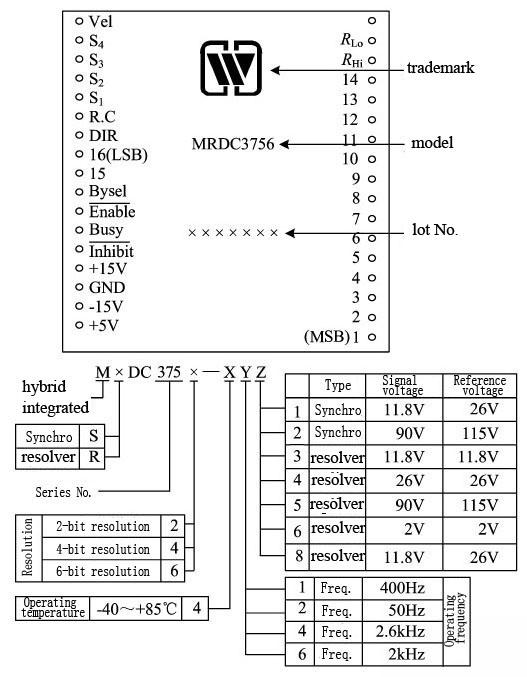

7 | D7 | 6. Pin-Bezeichnung von Synchro-Digital-Wandlern oder Resolver-Digital-Wandlern (MSDC/MRDC37-Serie) (Abb. 9, Tabelle 3) | 19 | S4 | Abb.9 Pin-Bezeichnung (Draufsicht) | 31 | Tabelle 3 Pin-Bezeichnung | Stift |

8 | D8 | Symbol | 20 | S3 | Bedeutung | 32 | Stift | Symbol |

9 | D9 | Bedeutung | 21 | S2 | Stift | 33 | Symbol | Bedeutung |

10 | Digitalausgang 1 (höchstes Bit) | D13 | 22 | S1 | Digitalausgang 13 | 34 | VL | D16 |

11 | Digitalausgang 16 | Digitalausgang 2 | 23 | D14 | Digitalausgang 14 | |||

12 | D15 | Digitalausgang 15 | 24 | Digitalausgang 3 | RHi |

Referenzsignaleingang (Low-End) | Signal aktivieren | Digitalausgang 5 | Sackgasse | Belebt | Besetztzeichen |

Digitalausgang 6 | Vel | 7 | Geschwindigkeitsspannungsausgang | 13 | Sperrsignal |

2 | Digitalausgang 7 | 8 | Signaleingang | 14 | +Vs |

3 | +15V Stromversorgung | 9 | Digitalausgang 8 | 15 | Signaleingang |

4 | Masse | 10 | Stromboden | 16 | Digitalausgang 9 |

5 | Signaleingang | 11 | -Vs | ||

6 | -15 V Stromversorgung | 12 | D10 |

| |

| Signaleingang | +5V Stromversorgung |

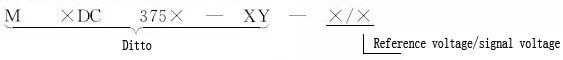

X

X