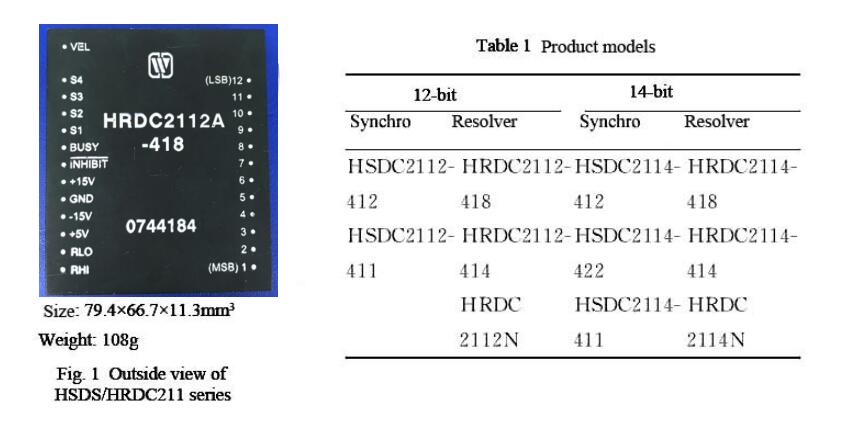

| Anregungsfrequenz 50Hz, 400Hz und 2,6kHz |  |

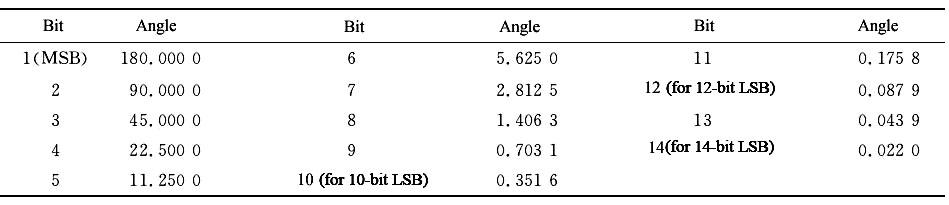

| Auflösung: 10 Bit, 12 Bit, 14 Bit | |

| Hohe Tracking-Geschwindigkeit | |

| Ein nicht standardmäßiger Eingang ist über einen externen Widerstand einstellbar oder wird am Produkteingangsanschluss angepasst | |

| Gleichspannungsausgang direkt proportional zur Winkelgeschwindigkeit | |

| Kompatibel mit der SDC1700-Serie der amerikanischen Firma AD |

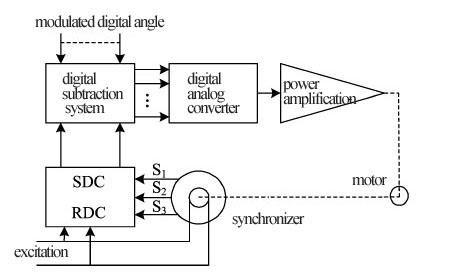

Wandlung. | Die Betriebsspannung beträgt ±15 V und + 5 V Gleichstrom. Es gibt zwei Arten von |

Ausgangssignal: dreizeiliges Synchro- und Referenzsignal (SDC-Wandler) | |

oder vierzeiliger Resolver und Referenzsignal (RDC-Wandler); die Ausgabe | |

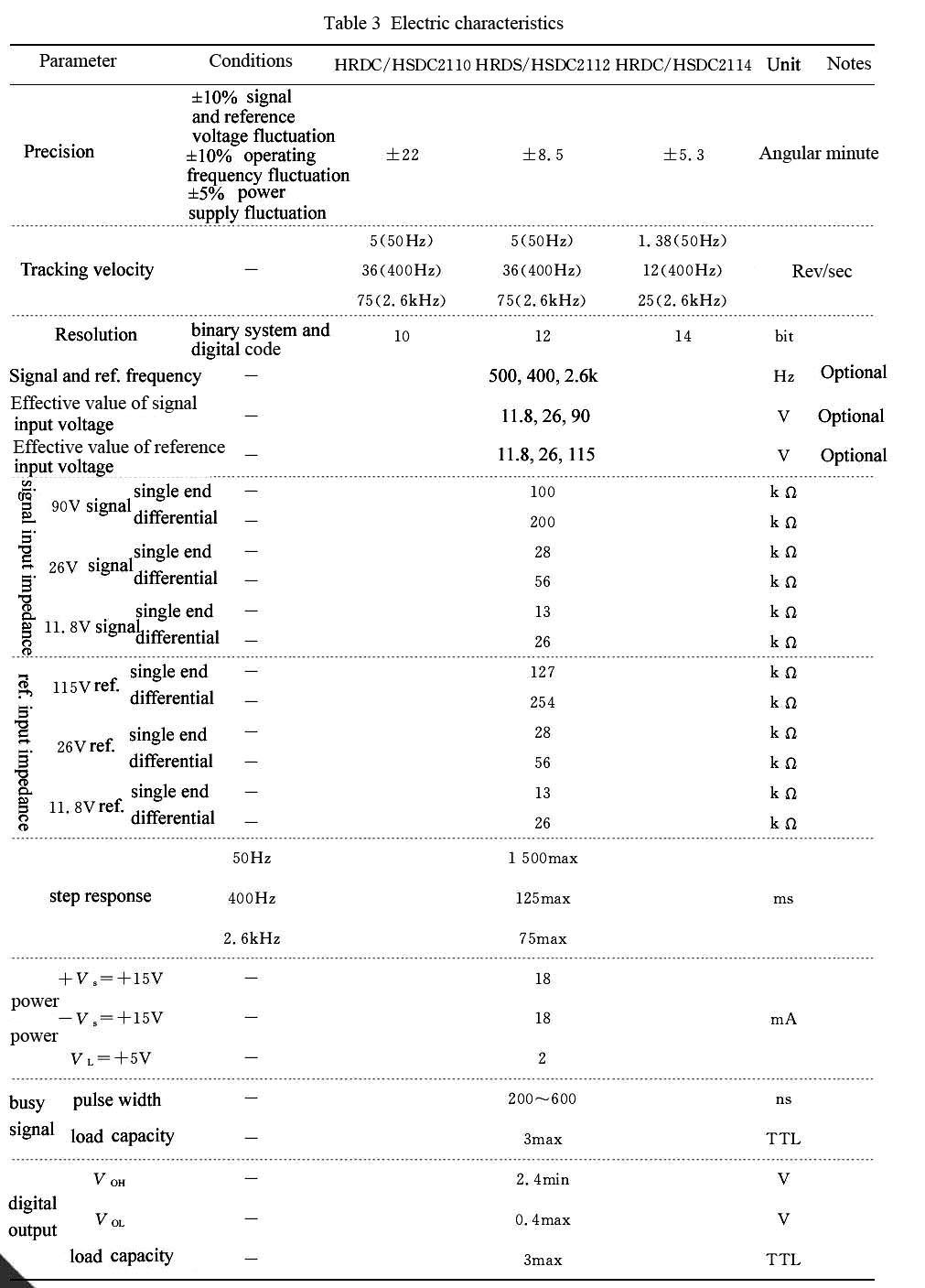

ist parallele digitale Codes des Binärsystems. | 4 Elektrische Leistung (Tabelle 2, Tabelle 3) von Synchro to |

Digitalwandler oder Resolver-zu-Digital-Wandler (HSDC/HRDC211 | |

Serie) | |

Tabelle 2 Nennbedingungen und empfohlene Betriebsbedingungen | |

Absolute max. Nennwert | |

Versorgungsspannung Vs: ± 17,5 V |

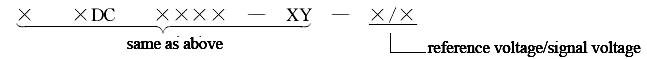

| Effektivwert der Referenzspannung VRef: 11,8 V, 26 V, 115 V Effektivwert der Referenzspannung V1*: 11,8 V, 26 V, 90 V |  Referenzfrequenz f*: 50 Hz, 400 Hz, 2,6 kHz |

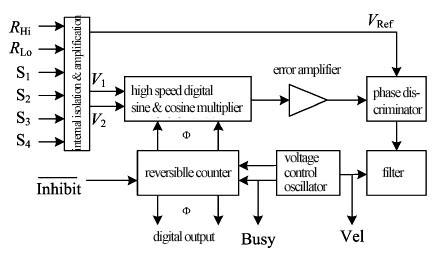

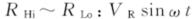

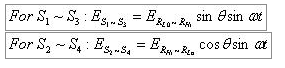

Wobei θ der analoge Eingangswinkel ist Das orthogonale Signal wird mit dem binären digitalen Winkel φ in der multipliziert Das orthogonale Signal wird mit dem binären digitalen Winkel φ in der multipliziert | interner reversibler Zähler in der Sinus-Cosinus-Funktion Multiplikator und |

θ-φ≠0, der spannungsgesteuerte Oszillator gibt Impulse aus, um die zu ändern | Daten im umkehrbaren Zähler, bis θ-φ innerhalb von Null wird |

|  |

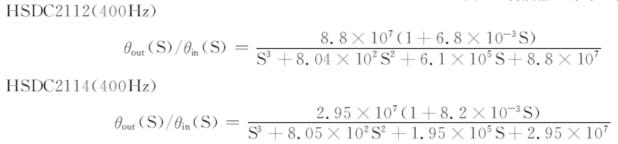

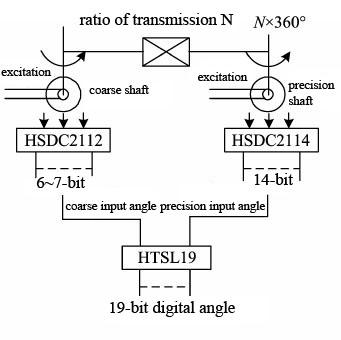

| Genauigkeit des Konverters, dabei folgt der Konverter der Änderung des Eingangswinkels θ die ganze Zeit. Zum Arbeitsprinzip siehe Abb. | 2. Übertragungsfunktion: Es folgen Parameter für die Übertragungsfunktion von HSDC2112 und HSDC2114 (400 Hz), für andere Modelle wenden Sie sich bitte an die Hersteller direkt. Abb.2 Blockdiagramm für das Funktionsprinzip des Konverters |

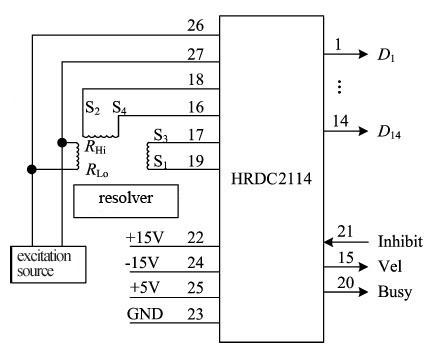

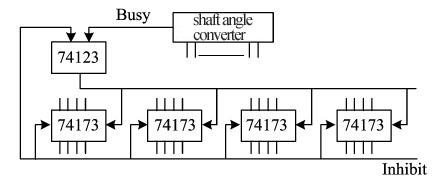

Es gibt zwei Methoden zum Auslesen der gültigen Daten des Konverters wie folgt: | Inhibit-Methode (synchrones Lesen): | Setzen Sie Inhibit auf logisch „0“, zu diesem Zeitpunkt stoppt der Konverter die Verfolgung. Warten auf | 1 μs, bis die Ausgangsdaten stabil sind, lesen Sie die Daten, die gelesenen Daten sind die | zu diesem Zeitpunkt gültig (1 μs wurde verzögert). Auf logisch „1“ gesetzt, beginnt der Konverter zu diesem Zeitpunkt erneut mit der Verfolgung, um sich auf das Lesen der nächsten gültigen Daten vorzubereiten. | Busy-Methode (asynchrones Lesen): Inhibit |

1 | D1 | Im asynchronen Lesemodus | 15 | auf logisch „1“ oder frei gesetzt, wenn die interne Schleife immer stabil ist | Status oder ob die Ausgabedaten gültig sind, wird durch die bestimmt |

2 | D2 | Zustand des Besetztzeichens Besetzt. Wenn das Besetztsignal auf hohem Pegel ist, wird es | 16 | S4 | zeigt an, dass die Daten konvertiert werden, und die Daten zu diesem Zeitpunkt werden konvertiert |

3 | D3 | instabil und ungültig; Wenn das Besetztsignal auf niedrigem Pegel ist, zeigt es an | 17 | S3 | Die Datenkonvertierung ist abgeschlossen und die Daten sind zu diesem Zeitpunkt stabil |

4 | D4 | und gültig. Im asynchronen Lesemodus ist der Busy-Ausgang eine Impulsfolge | 18 | S2 | TTL-Pegel, die Breite dazwischen bezieht sich auf die Drehzahl. Beziehen auf |

5 | D5 | Zeitablaufdiagramm der Datenübertragung Abb. 3. | 19 | S1 | Abb.3 Zeitlicher Ablauf der Datenübertragung |

6 | D6 | (2) Dämpfungsmethode des Eingangssignals | 20 | Wenn der vom Benutzer verwendete Synchro oder Resolver nicht dem Standard entspricht, um | Stellen Sie die Eingangssignalspannung und die Eingangserregungsspannung zusammen |

7 | D7 | Nennwerte des Konverters, der Benutzer kann die Methode übernehmen | 21 |

| externer Dämpfungswiderstand in Reihe geschaltet, d.h. für jeweils 1V |

8 | D8 | bei Überschreitung des Nennwertes 1,1kΩ Widerstand in Reihe an den schalten | 22 | entsprechende Eingangsklemme. Bei Verwendung des Konverters wird die Serie | Widerstand an jedem Anschluss muss genau ausgewählt und bereitgestellt werden, |

9 | D9 | und Widerstandsmaterial der gleichen Charge angenommen werden, um sicherzustellen | 23 | die Konvertierungsgenauigkeit des Konverters innerhalb des weiten Temperaturbereichs | Bereich, für alle 0,1% wird der Anpassungsfehler des Serienwiderstands |

10 | 1,7 Winkelminuten-Umwandlungsfehler erzeugen. | Es wird vom Hersteller empfohlen, dies vorzugsweise zu melden | 24 | der Hersteller, um die Nicht-Standard-Synchro oder Resolver als anzupassen | nach den erforderlichen Parametern, wenn der Benutzer sie verwendet. |

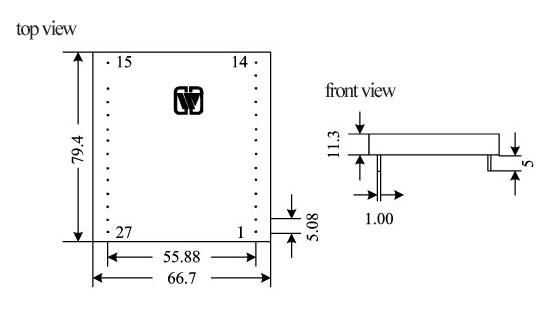

11 | 6 MTBF-Kurve (Abb. 4) von Synchro-Digital-Wandlern oder Resolver-Digital-Wandlern (HSDC/HRDC211-Serie) | 7 Pin-Bezeichnung (Abb. 5, Tabelle 4) von Synchro-Digital-Wandlern oder Resolver-Digital-Wandlern (HSDC/HRDC211-Serie) | 25 | Abb. 4 MTBF-Temperaturverlauf | (Anmerkung: nach GJB/Z299B-98, gute Bodenbeschaffenheit vorausgesetzt) |

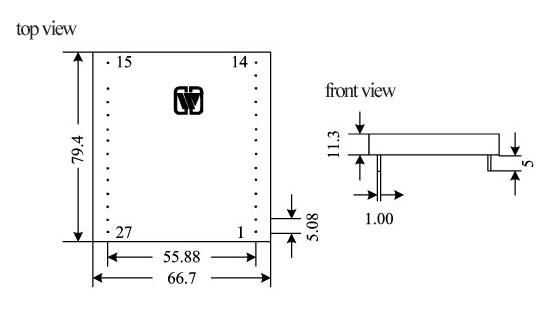

12 | Anmerkungen: | ① Die obige Struktur ist für HRDC2114 geeignet | 26 | ② für SDC, kein Pin S4 | ③ für 12-Bit-Gerät keine Pins 13 und 14, für 10-Bit-Geräte keine Pins 11, 12, 13 und 14. |

13 | Abb.5 Pin-Bezeichnung (Draufsicht) | Tabelle 4 Pin-Bezeichnung | 27 | Stift | Symbol |

14 | Funktion | Stift |

| Signaleingang Digitaler Ausgang von Bit 6 Belebt Besetztsignaleingang |  |

| Digitaler Ausgang von Bit 7 |

| -15V |  -15 V Stromversorgung |

D11 |

|  |

| +5V Stromversorgung | D12 |

X

X