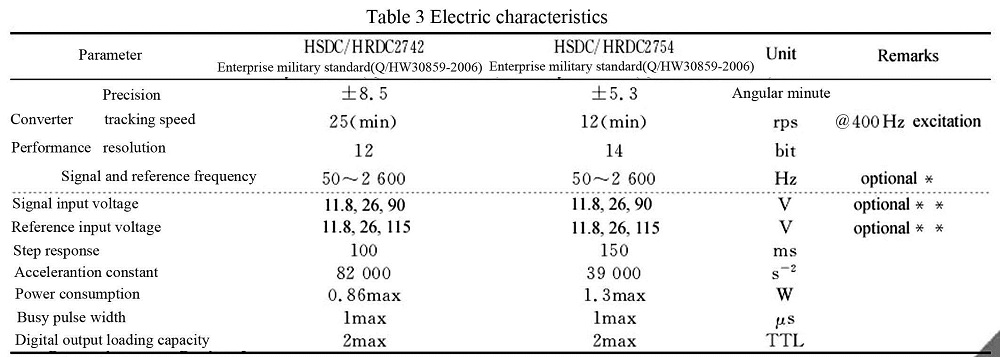

Die Betriebsleistung beträgt ±15 V und + 5 V Gleichstrom. Es gibt zwei Arten von Ausgangssignalen: dreizeiliges Synchro- und Referenzsignal (SDC-Konverter) oder vierzeiliges Resolver- und Referenzsignal (RDC-Konverter); Der Ausgang nimmt parallele digitale Codes des Binärsystems an.

| Auflösung: 12 Bit, 14 Bit |  |

| Hohe Tracking-Geschwindigkeit | |

| Hybrid-Integration, Metallgehäuse | |

| Latch-Ausgang mit drei Zuständen | |

| Mit Geschwindigkeitssignal Vel Ausgang | |

| Unbegrenzte Kompatibilität mit der AD1740-Serie |

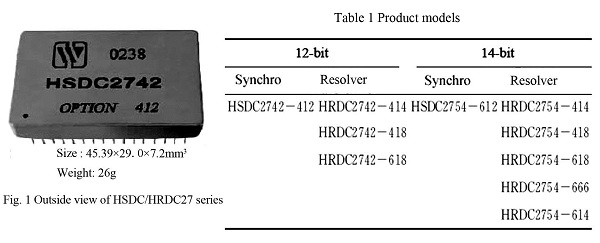

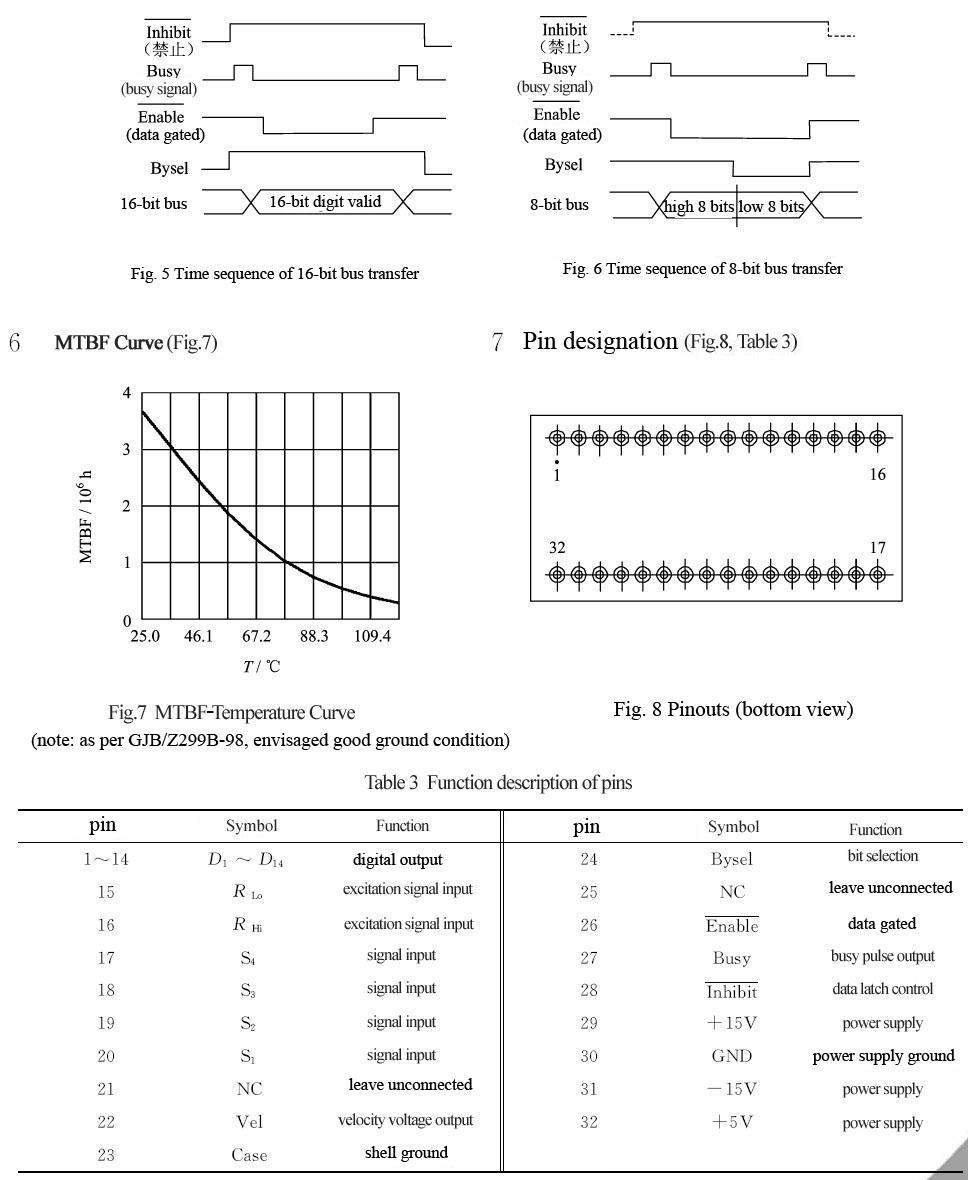

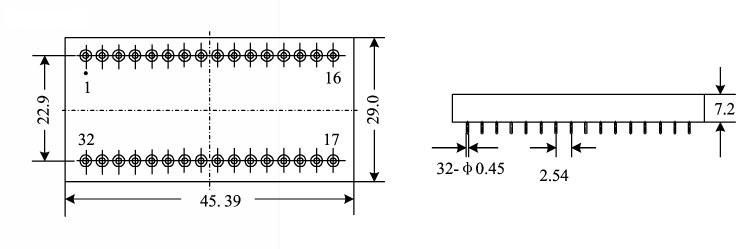

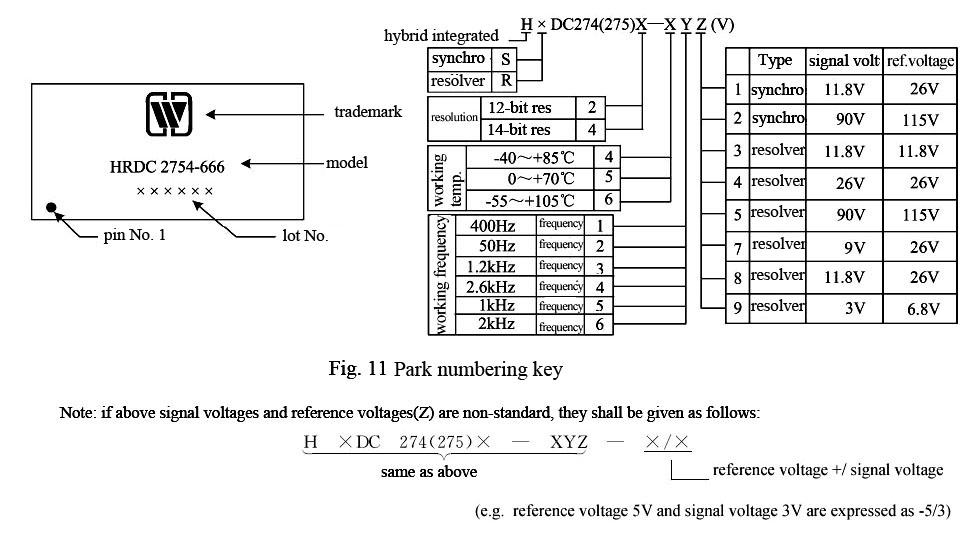

Die HSDC/HRDC27-Serie ist ein Digital-zu-Synchro-Wandler oder Resolver-zu-Digital-Wandler für die kontinuierliche Verfolgung von Typ-II-Servoschleifen. Er speichert und gibt natürlich binär codierte 12-Bit- oder 14-Bit-Daten mit 32-Zeilen-Dual-in-Line-Metall parallel Paket, zeichnet sich durch die Vorteile von kleinem Volumen, geringem Gewicht und hoher Zuverlässigkeit usw. aus und wird häufig in automatischen Steuersystemen wie Radarsystemen, Navigationssystemen usw. eingesetzt.

Die Betriebsleistung beträgt ±15 V und + 5 V Gleichstrom. Es gibt zwei Arten von Ausgangssignalen: dreizeiliges Synchro- und Referenzsignal (SDC-Konverter) oder vierzeiliges Resolver- und Referenzsignal (RDC-Konverter); Der Ausgang nimmt parallele digitale Codes des Binärsystems an.

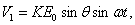

Tabelle 2 Nennbedingungen und empfohlene Betriebsbedingungen

Absolute max. Nennwert | Versorgungsspannung Vs: ± 17,5 V |

Logische Spannung VL: +5,5 V | |

Lagertemperaturbereich: -55℃~+125℃ | |

Empfohlene Betriebsbedingungen | Versorgungsspannung Vs: ± 5 V |

Logische Spannung VL: 5 V | |

Effektivwert der Referenzspannung VRef: ±10 % des Nennwerts | |

Gültigkeit der Signalspannung V1*: ±5 % des Nennwerts | |

Referenzfrequenz f*: 50 Hz bis 2,6 kHz | |

Betriebstemperaturbereich TA: -40~+85℃,-55~+105℃ |

Hinweis: * zeigt an, dass es nach Anforderung des Benutzers angepasst werden kann.

| Ausgang; 12-Bit- oder 14-Bit-Daten lesen; Inhibit auf logisch „1“ setzen, um |  |

| 16-Bit-Übertragung). | B: Der Konverter ist mit dem 8-Bit-Bus verbunden, die Bits D1 bis D8 sind mit dem Datenbus verbunden und der Rest ist leer. |

| |

| Hemmen ist | |

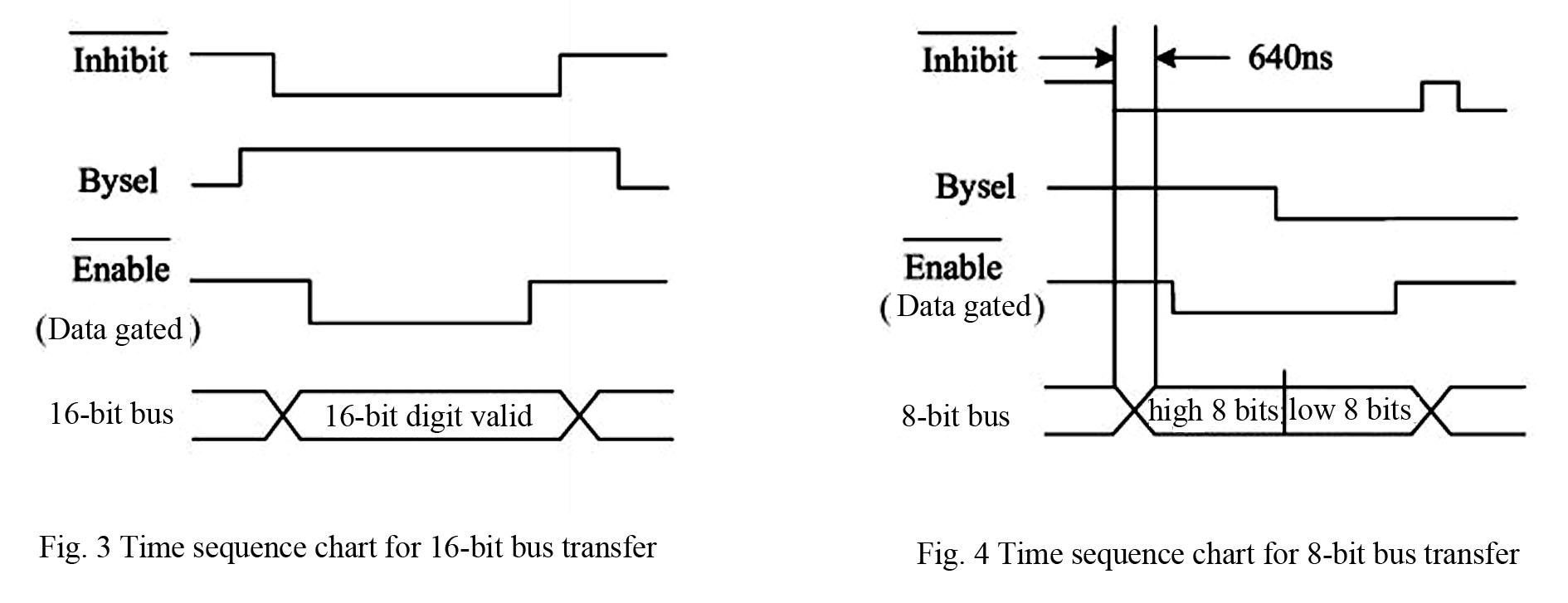

| Aktivieren auf logisch „0“, die Latch-Daten im Konverter dürfen | ausgegeben werden; wenn Byse1 auf logisch „1“ gesetzt ist, liest der Konverter direkt | die höheren 8-Bit-Daten, wenn Byse1 auf logisch „0“ gesetzt ist, liest der Konverter | die Restbits, fügt automatisch Null für unvollständige Bits hinzu; Setzen Sie die Sperrdatensperrsteuerung (Sperrsignal) auf logisch „1“, um sich auf das Lesen der nächsten gültigen Daten vorzubereiten (siehe Abb. 3 und Abb. 4 für die 8-Bit-Übertragungszeitsequenz). | (2) Busy-Methode (asynchrones Lesen): | Im asynchronen Lesemodus wird die Datensperrsteuerung (Sperrsignal) auf logisch „1“ oder leer gesetzt, unabhängig davon, ob die interne Schleife immer eingeschaltet ist | der stabile Zustand oder ob die Ausgangsdaten gültig sind, soll bestimmt werden | durch den Zustand des Besetztzeichens Besetzt. Wenn das Besetztsignal hoch ist | Ebene zeigt es an, dass die Daten konvertiert werden, und die Daten auf dieser Ebene |

| Zeit ist instabil und ungültig; wenn das Besetztsignal auf niedrigem Pegel ist, es | zeigt an, dass die Datenkonvertierung abgeschlossen ist, und die Daten dabei | Au | Zeit ist stabil und gültig. Sobald während des Lesens ein hoher Pegel in Busy auftritt, | Au | die Ablesung dieser Zeit ist ungültig. Im asynchronen Lesemodus Busy | Au | Der Ausgang ist eine Impulsfolge mit TTL-Pegel, die Breite dazwischen bezieht sich auf | Drehzahl. Ebenso finden sich auch 8-Bit und 16-Bit zwei Verwendung |

X

X