| Umwandlung mit interner Differenzisolation |  |

| 16-Bit-Auflösung | |

| Genauigkeit: 2 Winkelminuten | |

| Latch-Ausgang mit drei Zuständen | |

| Hohe kontinuierliche Tracking-Geschwindigkeit | |

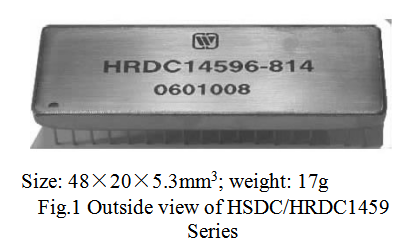

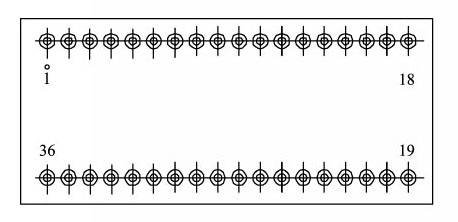

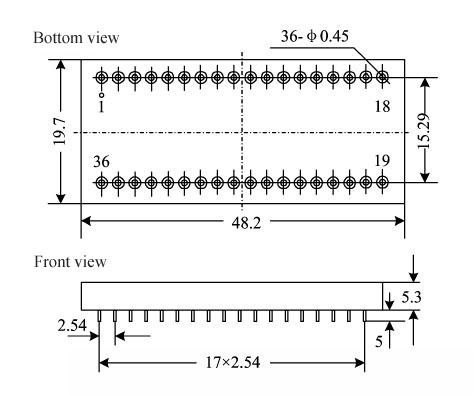

| 36-adriges, salznebelbeständiges, metallversiegeltes DDIP-Paket | |

| Pin-zu-Pin-kompatibel mit dem Modell SDC14560 der Firma DDC |

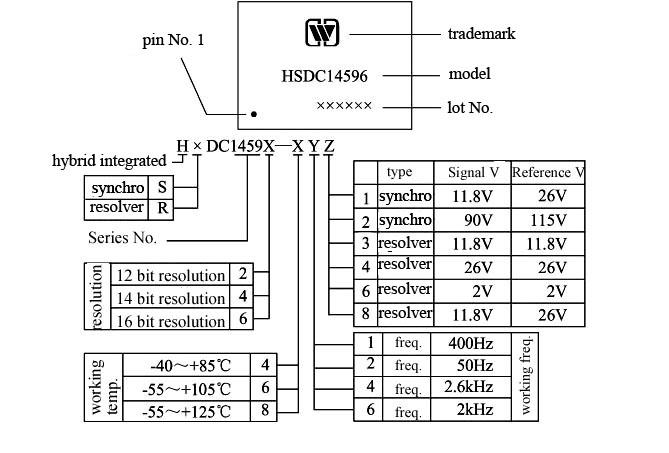

| Integriertes Konvertierungsgerät für kontinuierliches Tracking, das auf dem entwickelt wurde | Prinzip des Servomodells II. Diese Serienprodukte sind entworfen und |

| Hergestellt durch MCM-Prozess, nehmen die Kernelemente einen speziellen Chip an | |

| unabhängig von unserem Institut entwickelt. Die Pinbelegung ist | |

| kompatibel mit Produkten der SDC14560-Serie der amerikanischen DDC-Firma, 16-Bit | |

| paralleler natürlicher Binärcode-Datenlatchausgang, insgesamt 36-Zeilen-DIP | |

| versiegeltes Metallgehäuse, haben die Vorteile von hoher Präzision, klein | |

| Lautstärke, geringer Stromverbrauch, geringes Gewicht und hohe Zuverlässigkeit usw., | und kann in wichtigen strategischen und taktischen Waffen wie z |

| Flugzeug, Marineschiff, Kanone, Rakete, Radar, Panzer usw. | |

| 4. Elektrische Leistung (Tabelle 1, Tabelle 2) | |

| Synchro-Digital-Wandler oder Resolver-Digital-Wandler (HSDC/HRDC1459-Serie) | |

| Tabelle 1 Nennbedingungen und empfohlene Betriebsbedingungen | |

| Absolute max. Nennwert |

| Signalspannung V1: Nennwert ±20 % | Referenzspannung VRef: Nennwert ±20 % | Betriebsfrequenz f: Nennwert ±20 % | |

| Lagertemperatur Tstg: -65 ~ 150 ℃ | Empfohlene Betriebsbedingungen | ||

| Logische Versorgungsspannung VL: 5±0,5 V | Versorgungsspannung Vs: 15 ± 0,75 V | ||

| Signalspannung V1: Nennwert ±10 % | Referenzspannung VRef: Nennwert ±20 % | Betriebsfrequenz f: Nennwert ±20 % | — |

| Betriebstemperaturbereich (TA): -55℃~125℃ | Hinweis: * gibt an, dass es gemäß den Anforderungen des Benutzers angepasst werden kann. | Tabelle 2 Elektrische Eigenschaften | Parameter |

| Bedingungen | — | HSDC14569 Serie | (VSu003d15 V, VLu003d+5 V) |

| Militärstandard (Q/HW20725-2006) | — | 2V | Mindest. |

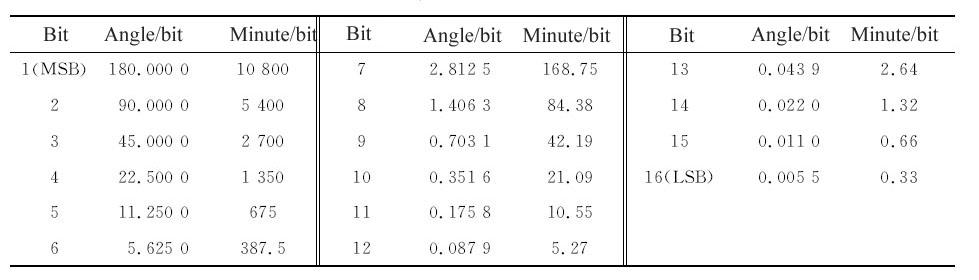

| max. | — | Auflösung | Paralleler digitaler Code des binären Systems |

| 16 Bit | — | 2V | Genauigkeit |

| ± 10 % von Signalspannung, Referenzspannung und Schwankungsbereich der Betriebsfrequenz | — | -2 Winkelminuten | +2 Winkelminuten |

| Bereich der Referenzfrequenz | — | 50Hz | 2600Hz |

| Bereich der Referenzspannung | — | 115V | Referenz-Eingangsimpedanz |

4,4 kΩ 4,4 kΩ | — | 0 | 129,2 kΩ |

Bereich der Signalspannung Bereich der Signalspannung | — | 0 | 90V |

Signaleingangsimpedanz Signaleingangsimpedanz | — | 0 | 4,4 kΩ |

| 102,2 kΩ | — | Signal-/Referenzphasenverschiebung | —70° |

| +70° | — | Eingangslogikebene | Logik „1“ ≥3,3 V |

| Logik „0“ ≤0,8 V | — | Eingang | 0,8 V |

| Eingang | — | 0,8 V | |

| Eingang | — | — | 0,8 V |

| Ausgangslogikebene | — | — | Logik „1“ ≥3,3 V |

| Logik „0“ ≤0,8 V | — | — | Ausgabe des digitalen Winkelcodes |

| Logik „1“ ≥3,3 V | — | — | Logik „0“ ≤0,8 V |

| Konvertieren der Besetztzeichen-Ausgabe (CB). | — | 200ns | 600ns |

| Fehlererkennungs-Bit-Ausgang | Logik „0“ zeigt Fehler an | — | Ladekapazität |

| 3TTL | Tracking-Geschwindigkeit | ||

| 2,5 U/s | Beschleunigung konstant | ||

| +10V Strom UVu003d+15V 10mA |  VS u003d 15 V |

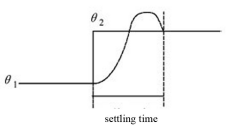

Geschwindigkeit. Der Oszillationsprozess des ausgegebenen digitalen Winkels ist in dargestellt

Geschwindigkeit. Der Oszillationsprozess des ausgegebenen digitalen Winkels ist in dargestellt 6. Funktionsprinzip (Abb. 3)

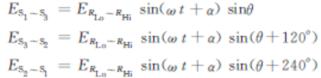

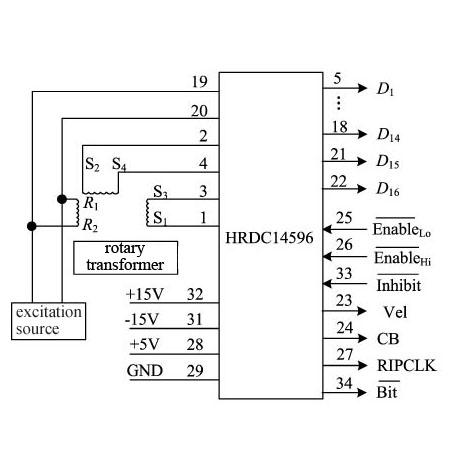

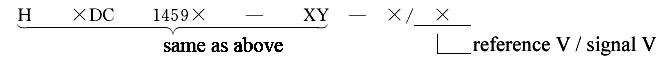

6. Funktionsprinzip (Abb. 3)| Synchro-Digital-Wandler oder Resolver-Digital-Wandler (HSDC/HRDC1459-Serie) Das Eingangssignal des Synchro (oder Resolvers) wird durch die interne differenzielle Trennung in das orthogonale Signal gewandelt: | |

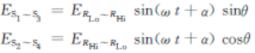

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofWobei θ der analoge Eingangswinkel ist. Abb. 2 Kurve der Sprungantwort | Diese beiden Signale und der digitale Winkel φ des internen Umkehrzählersof werden im Multiplikator von Sinus- und Cosinus-Funktionen multipliziert und sind Fehler behandelt: |

| Verstärkung, Phasendiskriminierung und Integrationsfilterung, wenn | θ-φ≠0, der spannungsgesteuerte Oszillator gibt die Impulse aus, und die | umschaltbarer Zähler zählt, bis θ-φ innerhalb der Genauigkeit von Null wird | Der Konverter, während dieses Prozesses, verfolgt die Konvertierung die Änderung von | Eingangswinkel die ganze Zeit. | Lesemethode: |

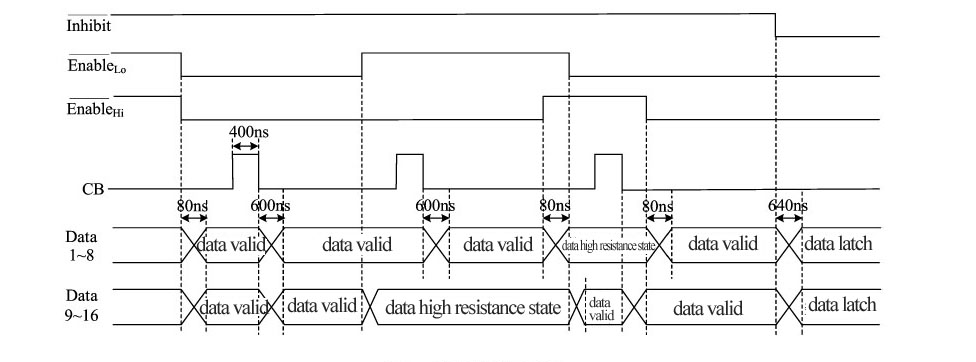

| 1 | S1 | Für die Datenübertragung stehen folgende zwei Methoden zur Verfügung: | 25 |  | (1) Sperrmethode: |

| 2 | S2 | Nach 640 ns von | 26 |  | logisch niedrig, die Ausgangsdaten sind gültig und der Konverter realisiert die Datenübertragung durch |

| 3 | S3 | und | 27 | . Nachdem die Sperrung aufgehoben wurde, generiert das System automatisch einen Impuls mit einer Breite, die dem Besetztimpuls für die Datenaktualisierung entspricht. | (2) Bust-Modus: |

| 4 | S4 | An der ansteigenden Flanke des Beschäftigt-Impulses zählt der dreistufige umkehrbare Zähler; an der absteigenden Flanke des Busy-Impulses erzeugt er intern einen Latch-Impuls mit einer Breite gleich dem Busy-Impuls zum Aktualisieren der Daten des Drei-Zustands-Latches der Busy-Logik niedrig ist die stabile Datenübertragung gültig. Im asynchronen Lesemodus ist die Beschäftigt-Ausgabe eine Impulsfolge auf CMOS-Ebene. Die Breite des hohen und niedrigen Pegels hängt von der Betriebsfrequenz und der Rotationsgeschwindigkeit des ausgewählten Geräts ab. | 28 | VL | Abb.4 Zeitlicher Ablauf der Datenübertragung |

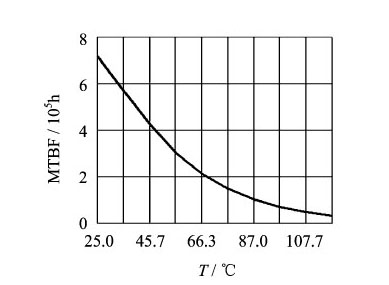

| 7. MTBF-Kurve (Abb. 5) | Synchro-Digital-Wandler oder Resolver-Digital-Wandler (HSDC/HRDC1459-Serie) | Abb. 5 MTBF-Temperaturkurve | 29 | 8. Pin-Bezeichnung (Abb. 6, Tabelle 3) | Synchro-Digital-Wandler oder Resolver-Digital-Wandler (HSDC/HRDC1459-Serie) |

| 19 | Abb.6 Pin-Bezeichnung (Ansicht von unten) | (Anmerkung: nach GJB/Z299B-98, gute Bodenbeschaffenheit vorausgesetzt) | 30 | NC | Tabelle 3 Pin-Bezeichnung |

| 20 | RL | Stift | 31 | Symbol | Bedeutung |

| 21 | Stift | Symbol | 32 | VS | Bedeutung |

| 22 | Resolver-Eingang S1 (oder Synchro-Eingang S1) | Digital aktivierte Steuerung der unteren 8 Bits | 33 | Resolver-Eingang S2 (oder Synchro-Eingang S2) | Digitale aktivierte Steuerung höherer 8 Bits |

| 23 | Resolver-Eingang S3 (oder Synchro-Eingang S3) | RIPCLK | 34 | Null-Bit-Signalausgabe | Resolver-Eingang S4 (unverbunden lassen) |

| 24 | CB | +5 V Stromversorgung | 18. Mai | NC | D1-D14 |

| Digitaler Ausgang 1 (MSB)-14 | Masse |

| Boden | RHi |

| High-End-Referenzsignaleingang | Keine Verbindung |

| RL | Niedriges Ende des Referenzsignaleingangs |

-VS

-VS -15 V Stromversorgung

-15 V Stromversorgung

D15 Digitaler Ausgang 15

Digitaler Ausgang 15 ).

).

+15 V Stromversorgung

D16

Digitaler Ausgang 16 (LSB)

Hemmen

Statischer Signaleingang

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Niedriges Ende des ReferenzsignaleingangsofNiedriger | 8-Bit-Ziffern-aktivierter Signaleingang, dieser Pin ist der logische Eingangspin vonofData-Gating-Steuerung, ihre Funktion besteht darin, eine Drei-Zustands-Steuerung durchzuführen |

|  |

| extern auf die unteren 8-Bit-Ausgangsdaten des Konverters. Niedriges Niveau ist | gültig, die unteren 8-Bit-Ausgangsdaten des Konverters belegen die Daten |

Widerstandszustand, und das Gerät belegt den Datenbus nicht. Ermöglichenund die Freigabeverzögerungszeit beträgt 600 ns (max.). | höher | 8-Bit-Ziffern-aktivierter Signaleingang, dieser Pin ist der logische Eingangspin von | Data-Gating-Steuerung, ihre Funktion besteht darin, eine Drei-Zustands-Steuerung durchzuführen | extern auf die höheren 8-Bit-Ausgangsdaten des Konverters. Niedriges Niveau | gültig ist, belegen die höheren 8-Bit-Ausgangsdaten des KonvertersDatenbus; Bei High-Pegel liegt der Pin der höheren 8-Bit-Ausgangsdaten auf High | Widerstandszustand, und das Gerät belegt den Datenbus nicht. Ermöglichen | und die Freigabeverzögerungszeit beträgt 600 ns (max.). | Hemmen Sie Statik |

Signaleingang, dieser Pin ist der Eingangspin der Steuerlogik, seine Funktion | Optional ist die Datenausgabe extern an den Konverter zu realisieren | NiVerriegelungs- oder Bypass-Steuerung. Auf hoher Ebene werden die Ausgangsdaten der | Konverter gibt direkt ohne Latchen aus; bei niedrigem Pegel der Ausgang | Daten des Konverters gelatcht werden, die Daten werden nicht aktualisiert, aber dieinterne Schleife wird nicht unterbrochen, und die Verfolgung funktioniert alle | Zeit hat Inhibit intern einen Pull-up-Widerstand zugeschaltet. Nach 600 ns (max.) Verzögerung von | Au fallende Flanke des statischen Signals, die Daten werden stabil (ob die | Gerät den Datenbus belegt, d.h. wann es die Daten ausgibt, hängt davon abauf dem Stand von | undCB „Besetzt“-Signalausgang, dieses Signal zeigt an, ob der Binärcode |

X

X