| Komplettes 2-Gang-System |  |

| Programmierbare Geschwindigkeitsverhältnisse im Grob-/Feinkanal | |

| 1:8, 1:16, 1:32, 1:64 | |

| Digitalausgang mit 3-State-Latches | |

| Die maximale Auflösung beträgt 20 Bit | |

| Die maximale Genauigkeit beträgt 5 Bogensekunden |

| Grob/Fein-Zweiwegesynchronisation zu Digitalwandlern oder Resolver enthalten |

|

| digitale Wandler und logische Fehlerkorrekturschaltung erforderlich durch zwei |

Geschwindigkeitsverhältnisse der Grob/Fein-Kombination der Produkte der Serie HTS20 sind | 1:8, 1:16, 1:32, 1:64, das erforderliche Geschwindigkeitsverhältnis kann durch erhalten werden | externes Programm. Es ist bequem zu bedienen. Grob/Fein-Eingang in zwei Richtungen Signale sind Signale von Dreileiter-Synchro oder Vierleiter-Resolver. Serie HTS20 programmierbarer 2-fach SDC/RDC-Wandlerausgang natürlich | Parallele Binärcodes. Das Maximum beträgt bis zu 20 Bit. Sie haben 3 Zustände | Riegel. | |

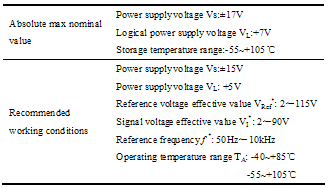

4 TECHNISCHE SPEZIFIKATIONEN von Synchro-Digital-Wandlern bzw | Resolver-zu-Digital-Wandler Serie HTS20 Programmierbarer SDC/RDC mit zwei Geschwindigkeiten | ||||

Konverter (Tab 2, Tab 3) | Tabelle 2 Nennbedingungen und empfohlene Betriebsbedingungen * bedeutet, dass es auf Bestellung gefertigt werden kann. Tabelle 3 Elektrische Eigenschaften Eigenschaften Bedingungen | - - - - | 17 18 19 20 | HTS20R/HTS20S | |

Geschäftlicher militärischer Standard | (Q/HW30925-2006) Einheiten Bemerkungen Mindest max | - - - - | 40 20 10 5 | Auflösung | |

(optional gesteuert von SC1, SC2) Geschwindigkeitsverhältnis 1:8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 Bit 90 | Genauigkeit (0°~360°) Hz V V | |

|  |

10k 115 | |

,

, Resolver-zu-Digital-Wandler Serie HTS20 Programmierbarer SDC/RDC mit zwei Geschwindigkeiten

Resolver-zu-Digital-Wandler Serie HTS20 Programmierbarer SDC/RDC mit zwei Geschwindigkeiten Konverter (Abb. 2, Abb. 3)

Konverter (Abb. 2, Abb. 3) ,

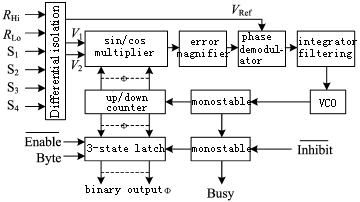

, (1) Single-Speed-Wandler

(1) Single-Speed-Wandler Die Funktionsprinzipien des Single-Speed-Konverters sind in Abb. 2 dargestellt. Die Prinzipien sind wie folgt zusammengefasst:

Die Funktionsprinzipien des Single-Speed-Konverters sind in Abb. 2 dargestellt. Die Prinzipien sind wie folgt zusammengefasst: Wobei θ der analoge Eingangswinkel ist.

Wobei θ der analoge Eingangswinkel ist. ,

, Die beiden Signale werden mit dem digitalen Winkel φ des internen Auf/Ab multipliziert

Die beiden Signale werden mit dem digitalen Winkel φ des internen Auf/Ab multipliziert .

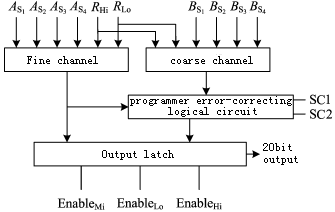

.Die Funktionsprinzipien des 2-Gang-Umrichters sind in Abb. 3 dargestellt. Das | Betrieb des Grob- und Feinkanals des 2-Stufen-Wandlers ist die |

|  |

| wie oben erwähnter Singlespeed, besteht aber aus 2-Speed-Konverter zwei Sätze von Single-Speed-Konverter und Programmiererfehler logisch Schaltkreis. Der Grobkanal erfüllt die Konvertierung aus dem logischen Winkel von 10 bis 12 Bit | |

Winkel zu digitalem Winkel. digitale Winkel konvertiert durch Grobkanal und | Feine Kanäle werden in die Fehlerkorrekturlogik des Programmierers eingegeben | Schaltung bzw. Nach der Fehlerbearbeitung und -behebung wird es | gibt eine parallele 20-Bit-Binärziffer aus, die in den Ausgang eingegeben wird | Latch und gepuffert, um den digitalen Winkel auszugeben und das Ganze zu erfüllen | Wandlung. | |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Abbildung 2 Funktionsblockdiagramm Abbildung 3 Funktionsblockdiagramm des Single-Speed-Wandlers des 2-Speed-Wandlers (3) Datenübertragungsverfahren und Timing Die Ausgänge der 2-Speed-Konverter der Serie HTS20 erreichen 20 Bit. Durch und die die 3-Zustands-Steuerung des Ausgangslatchs übernehmen, kann der 2-Geschwindigkeits-Wandler einfach an den Datenbus angeschlossen werden. und T1 T2 sind alle auf niedrigem Niveau gültig. EnableLo steuert die niedrigen 8 Bits, EnableMi steuert die mittleren 8 Bits, EnableHi steuert die hohen Restbits. Die Daten der 2-fach Umrichter der Serie HTS20 lauten wie folgt: Satz auf logisch „0“, nach 490μm sind Daten im 3-State-Latch des Wandlers aktualisiert. Es kann Daten mit niedrigen 8 Bit, mittleren 8 Bit und hohen Bits lesen durch Controlling und Abbildung 4 zeigt den Zeitpunkt des Lesens von Daten, wenn ein Wandler mit zwei Geschwindigkeiten und ein 8-Bit-Datenbus angeschlossen sind. Um eine hochgenaue Konvertierung des 2-Gang-Konverters zu gewährleisten, beachten Sie bitte Folgendes:

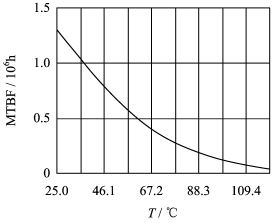

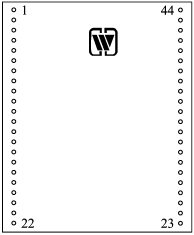

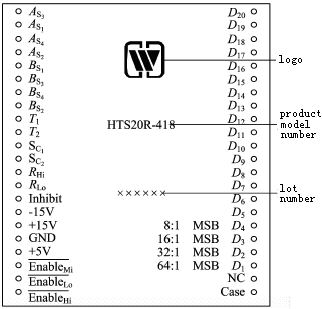

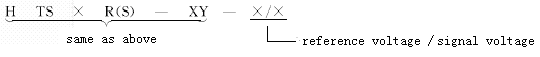

| Die Amplituden der Eingangssignale der Grob- und Feinkanäle sollten innerhalb des Nennwerts von 10 % garantiert werden. Frequenzen von Eingangssignalen und Referenzsignalen von groben und feinen Kanälen sollten die angegebenen Betriebsfrequenzen sein. Phasenverschiebung zwischen Eingangssignal und Referenzsignal grob Kanal und Phase zwischen Eingangssignal und Referenzsignal in Ordnung Kanal sollte kleiner als 10° sein. Wellenverzerrungen von Eingangssignalen und Referenzsignalen von groben und feinen Kanälen sollten weniger als 5 % betragen. Abweichungen von +5 V, ±15 V Stromversorgung sollten innerhalb von ±5 % garantiert werden. 6 MTBF-DIAGRAMM von Synchro-Digital-Wandlern bzw Resolver-zu-Digital-Wandler Serie HTS20 Programmierbarer SDC/RDC mit zwei Geschwindigkeiten Konverter (Abb. 5) 7-PIN-KONFIGURATIONEN von Synchro-Digital-Konvertern oder Resolver-zu-Digital-Wandler Serie HTS20 Programmierbarer SDC/RDC mit zwei Geschwindigkeiten Konverter (Abb.6, Tab4) Abbildung 5 MTBF vs. Temperatur Abbildung 6 Pin-Out-Draufsicht ( Hinweis: Gemäß GJB/Z 299B-98, vorausgesetzt dass der Boden in gutem Zustand ist) Tabelle 4 Pin-Beschreibung Stift Mnemonik Beschreibung Stift Mnemonik Beschreibung As3 As1 As4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | As2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 RHi RLo Hemmen -15V +15V Masse +5V Feiner Kanaleingang Feiner Kanaleingang | Feiner Kanaleingang Feiner Kanaleingang Grobkanaleingang Grobkanaleingang Grobkanaleingang Grobkanaleingang Einstellstift für Phasenverschiebung zwischen Signal und Referenz Einstellstift für Phasenverschiebung zwischen Signal und Referenz Programmsteuerstift für Grob und feine Geschwindigkeitsverhältnisse Programmsteuerstift für Grob und feine Geschwindigkeitsverhältnisse Eingangspin für Referenz hoch Eingangsstift für Referenz niedrig Sperrsignal -15 V Eingang +15V Eingang Boden +5V Eingang Aktivieren Sie mittlere 8-Bit-Daten | |

,

, D10

D10 D11

D11 D12

D12 D13

D13 D14

D14

Nicht verbunden Ausgabe des höchsten kombinierten digitalen Winkels | Ausgabe des kombinierten digitalen Winkels | Ausgabe des kombinierten digitalen Winkels Ausgabe des kombinierten digitalen Winkels | Ausgabe des kombinierten digitalen Winkels | Ausgabe des kombinierten digitalen Winkels Ausgabe des kombinierten digitalen Winkels | Ausgabe des kombinierten digitalen Winkels |

Ausgabe des kombinierten digitalen Winkels | Ausgabe des kombinierten digitalen Winkels | 8 | Ausgabe des kombinierten digitalen Winkels | 15 | Ausgabe des kombinierten digitalen Winkels |

2 | Ausgabe des kombinierten digitalen Winkels | 9 | Ausgabe des kombinierten digitalen Winkels | 16 | Ausgabe des kombinierten digitalen Winkels |

3 | Ausgabe des kombinierten digitalen Winkels | 10 | Ausgabe des kombinierten digitalen Winkels | 17 | Ausgabe des kombinierten digitalen Winkels |

4 | Ausgabe des kombinierten digitalen Winkels | 11 | Ausgabe des am wenigsten kombinierten digitalen Winkels | 18 | Notiz: |

5 | Pin3,7 der HTS20S sind nicht verbunden. | 12 | As1, As2, As3, As4 sind Feinkanaleingänge. Wenn Synchro mit drei Leitern ausgestattet ist, wird As4 nicht verwendet. | 19 | Bs1, Bs2, Bs3, Bs4 sind grobe Kanaleingänge. Wenn Synchro mit drei Drähten ausgestattet ist, wird Bs4 nicht verwendet. |

6 | RHi, RLo sind Referenzsignaleingänge. | 13 | Inhibit ist ein Sperrsignal, das über einen Pull-up-Widerstand mit der 5-V-Stromversorgung verbunden ist. Wenn Inhibit logisch „0“ ist, ist das Innere gesperrt. Nach 490 ns werden gültige Daten ausgegeben und können gelesen werden. Wenn logisch „1“ ist, stellt der Konverter den Tracking-Status wieder her, die ausgegebenen Daten sind ungültige Daten. | 20 | Hemmen |

7 | und | 14 | sind drei Zustandssteuerstifte der Datenausgabe, die den Zustand bestimmt |

Gehäuse ist Gehäusestift.

D1~D20 sind Ausgänge des kombinierten digitalen Winkels. D20 ist am wenigsten signifikant

Bit. Wenn das Geschwindigkeitsverhältnis 1:8 beträgt, ist D4 das höchstwertige Bit. Bei Geschwindigkeit | Verhältnis ist 1:16, D3 ist höchstwertiges Bit. Wenn das Geschwindigkeitsverhältnis 1:32 beträgt, D2 | ist das signifikanteste Bit. Wenn das Geschwindigkeitsverhältnis 1:64 beträgt, ist D1 am meisten | bedeutendes bisschen. 8-BIT-GEWICHTSTABELLE von Synchro-zu-Digital-Wandlern oder Resolvern | zu Digitalwandler HTS20-Serie Programmierbarer 2-Gang-SDC oder RDC Konverter ( Tab 5 ) | Tabelle 5: Bit-Gewichtstabelle | Bit | Anzahl Gewicht (Grad) | Bit |

Anzahl | Gewicht (Grad) Bit | Anzahl | Gewicht (Grad) | 1 (MSB) | 180.0000 1.1063 | 0,011 (40 Sek.) | 90.0000 |

|

|

| 45.0000 |

X

X